ПЛИС (FPGA) расшифровывается как "Field Programmable Gate Array" и представляет собой огромный массив вентилей, которые могут быть запрограммированы и перестроены в любое время и в любом месте. Многие пользователи до сих пор не понимают, что такое ПЛИС. «Огромный набор ворот» — упрощенное описание модели. Некоторые FPGA имеют встроенные жесткие блоки: контроллеры памяти, высокоскоростные коммуникационные интерфейсы и конечные точки PCIe. Внутри FPGA много вентилей, которые можно свободно соединить вместе. Принцип работы более или менее похож на подключение отдельных микросхем логических элементов. FPGA выпускаются ведущими компаниями мира Xilinx, Altera, и Microsemi.

История развития FPGA

Индустрия ПЛИС выросла из программируемой постоянной памяти PROM и логических устройств PLD. В 1970 г. Philips изобрел программируемую в полевых условиях матрицу. В конструкции такой ПЛИС, что состояла из двух планов, достигалась специфическая реализация логических схем: программируемая проводная "И" либо "ИЛИ". Это давало ей возможность реализации функции в виде Sum of Products.

Altera была создана в 1983 году, а уже в 1984 году выпустила первое в отрасли перепрограммируемое логическое устройство — EP300 с кварцевым окном в упаковке, что позволило использовать ультрафиолетовую лампу на матрице для удаления EPROM метки.

Чтобы преодолеть трудности стоимости и скорости, была разработана программируемая логика массива, в которую входил только один программируемый «И», вводимый в фиксированные «ИЛИ» ворота. PAL и PLA вместе с другими вариантами группируются как простые программируемые логические устройства SPLD. Такие ПЛИС, что интегрированы в один чип с предоставленными межсоединениями для программного соединения блоков, использовались для удовлетворения растущих технологических требований. Они названы комплексными PLD и разработаны Altera.

Транзисторы — другой класс электронных устройств, программируемых на основе масок массивов затворов. Они состоят из транзисторных массивов, которые могут быть подключены с помощью пользовательских проводов. Они уступили место логическим блокам, и теперь пользователь может выполнять настройку на месте, а не в производственной лаборатории.

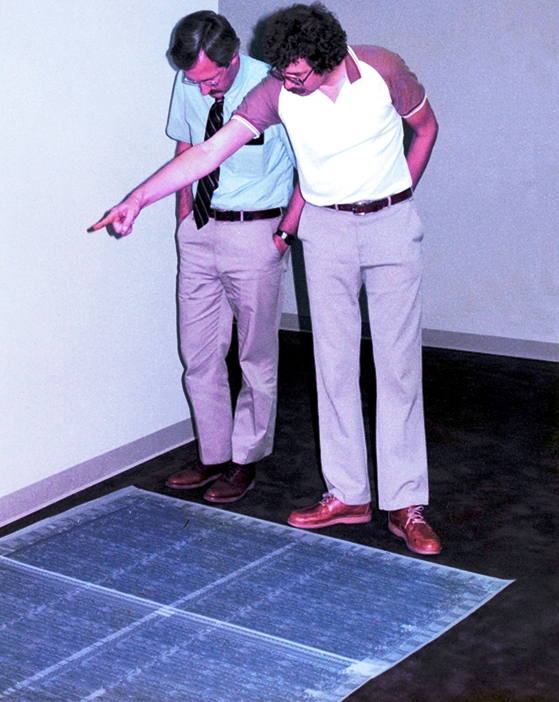

Идея разработки первой коммерчески жизнеспособной ПЛИС принадлежит соучредителям Xilinx Россу Фримену и Бернарду Вондершмитту. XC2064 был изобретен в 1985 году и состоял из 64 настраиваемых логических блоков с 3-мя справочными таблицами. Он дает современное понимание, что такое ПЛИС. Это было в конце 1980 года, когда предложенный Стивом Кассельман эксперимент по созданию компьютера с 6000000 перепрограммированных ворот нашел спонсоров в отделе надводных боевых действий ВМС США, а затем получил патент в 1992 году.

К концу 1990 года появилась большая конкуренция в производстве ПЛИС, тогда доля рынка Xilinx начала снижаться. Такие игроки, как Actel, Altera, Lattice, QuickLogic, Cypress, Lucent и SiliconBlue, заняли свою нишу на мировом рынке FPGA наряду с Xilinx. В 1997 году Адриану Томпсону удалось объединить программирование ПЛИСов и технологию генетического алгоритма с FPGA, начав новую эпоху Evolvable.

Сегодня ПЛИС стали достаточно доступными, в связи с чем продолжают завоевывать популярность на потребительских рынках. Они состоят из набора логических ячеек, называемых таблицами поиска LUT, окруженных межкомпонентной сетью, обеспечивающей гибкую систему, которая может реализовать практически любой цифровой алгоритм.

Принципы программирования

Программирование ПЛИС для начинающих — это процесс изучения, планирования, проектирования и реализации решения на FPGA. Количество и тип планировки варьируются от программы к программе. Создание документа с требованиями и создание документа с дизайном, с объяснением, как будет реализовано предлагаемое решение, может быть очень полезным для решения потенциальных проблем.

Время, затраченное на создание качественного проектного документа, сэкономит его в будущем на рефакторинге, отладке и исправлении ошибок. Реализация решения с помощью программирования ПЛИС включает в себя создание проекта с использованием одного из методов введения проекта. Среди них схемы или код HDL, например, Verilog или VHDL. FPGA могут запрограммировать выходной файл на физическое устройство FPGA с использованием инструментов программирования ПЛИС Altera. Введение дизайна с применением схем больше не используется в промышленности. Синтез и программирования почти полностью позаботились об инструментах вендора, таких как инструменты конфигурации ISE и Vivado и Numato Lab.

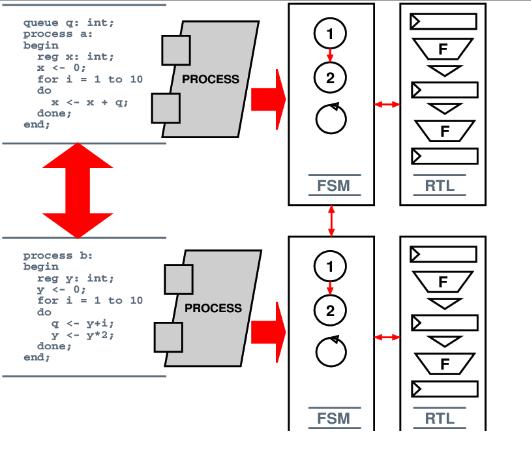

Уровень передачи регистра RTL

RTL обозначает уровень передачи регистра. Разработчик также может столкнуться с терминами Register Transfer Logic или Register Transfer Language, все они означают одно и то же в контексте проектирования оборудования. RTL — это абстракция более высокого уровня для цифрового аппаратного дизайна, которая находится где-то между строго поведенческим моделированием на одном конце и чисто структурным на уровне шлюза — на другом.

Моделирование гейтов означает описание аппаратных средств с использованием базовых вентилей, что является достаточно утомительным. RTL можно рассматривать как аналог термина «псевдокод», используемого в основах программирования ПЛИС. Можно описать аппаратный дизайн как последовательность шагов или потока данных от одного набора регистров к следующему в каждом тактовом цикле.

RTL также называют дизайном «потока данных». Как только проект RTL готов, его легче превратить в реальный код HDL, используя такие языки, как Verilog, VHDL, SystemVerilog или любой другой язык описания оборудования.

ПЛИС — это гораздо больше, чем просто множество ворот. Хотя можно строить логические схемы любой сложности, организуя и соединяя логические элементы. Это способ выразить логику в простом формате, который в конечном итоге можно превратить в массив элементов. Два популярных метода сделать это: введение схемы и языка описания оборудования HDL. До того, как он стал широко используемым, инженеры проектировали все с помощью схем. Они были очень простыми для небольших проектов, но болезненно неуправляемыми — для крупных. Стоит только представить себе, как инженеры Intel рисуют схемы для Pentium, у которого миллионы шлюзов! Это неприемлемо сложно.

Verilog — это язык описания аппаратных средств HDL, который можно использовать для цифровых схем в текстовом виде. Изучение Verilog не так сложно, если у пользователя есть опыт программирования. VHDL является еще одним популярным HDL, широко используемым в отрасли. Verilog и VHDL имеют более или менее одинаковое признание на рынке, но пользователи обычно выбирают Verilog, поскольку он прост в изучении и имеет синтаксическое сходство с языком Си.

Технологии программирования

ПЛИС можно считать строительными блоками, которые позволяют осуществить нужную настройку оборудования. Это особая форма PLD с более высокой плотностью и расширенными возможностями функционала за более короткий промежуток времени с использованием CAD. ПЛИС доступны в различных вариантах на основе используемой технологии программирования.

Они могут быть запрограммированы с использованием:

- Antifuse Technology.

- Программирование на основе технологии Flash как устройства от Actel.

- FPGA может быть перепрограммирован несколько тысяч раз, что занимает несколько минут в самом поле для перепрограммирования и имеет энергонезависимую память.

ПЛИС на основе технологии SRAM, которая предлагает неограниченное перепрограммирование и очень быструю реконфигурацию или частичную реконфигурацию во время самой работы с небольшим количеством дополнительных схем. Большинство таких компаний, как Altera, Actel, Atmel и Xilinx, производят эти устройства.

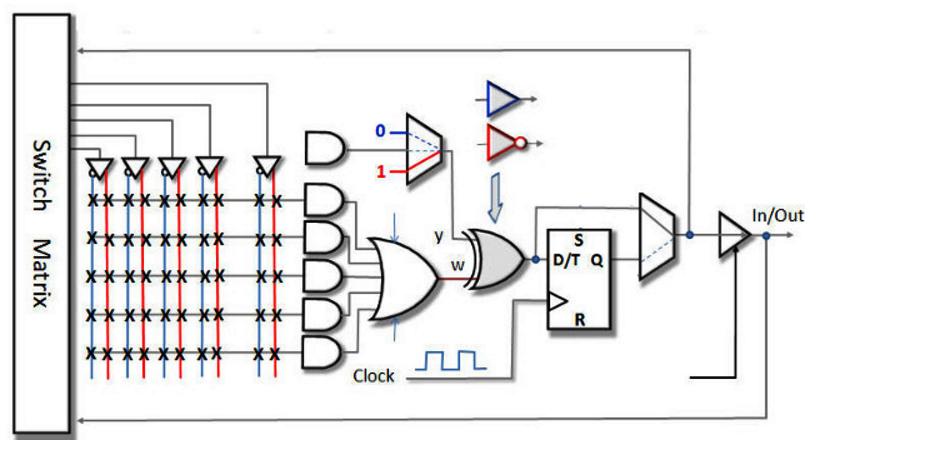

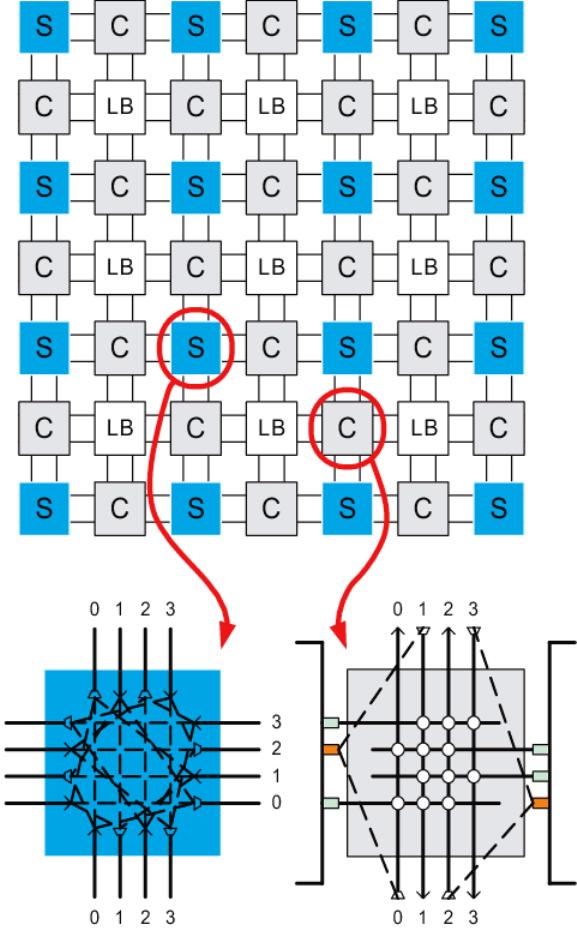

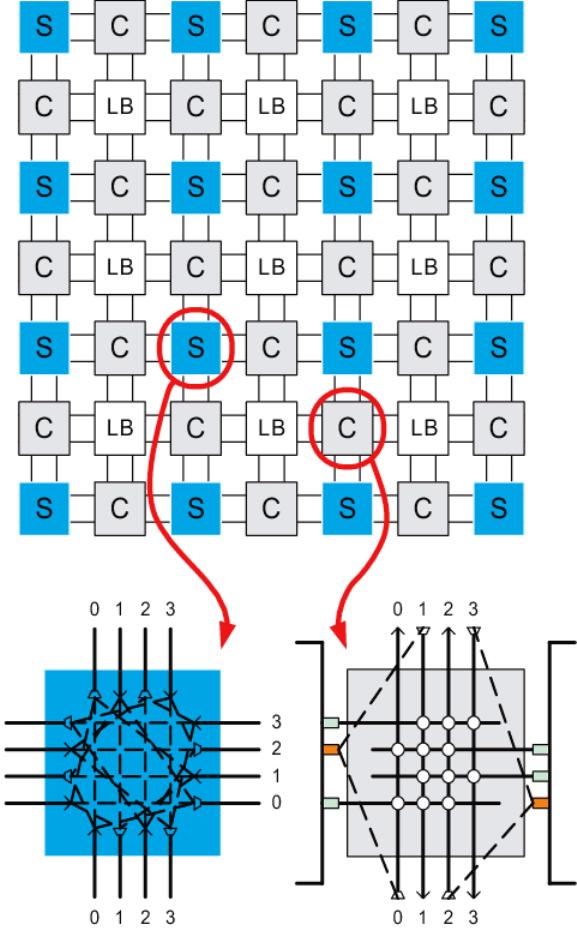

Конфигурируемые логические блоки

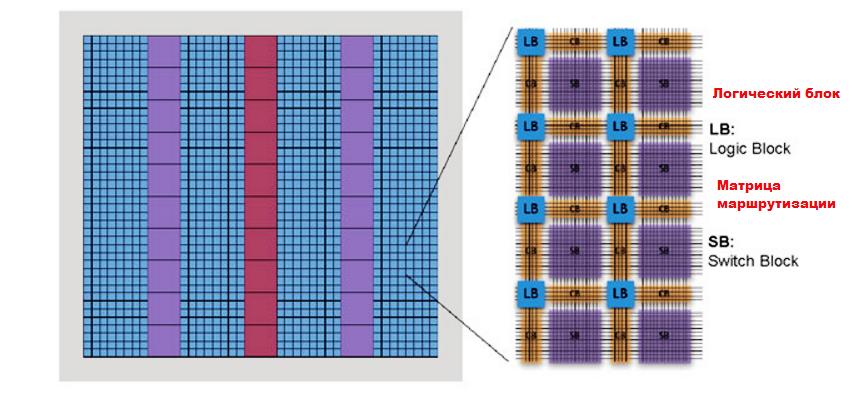

Независимо от различных производителей и несколько разных архитектур и наборов функций, большинство FPGA имеет общий подход. Основными компонентными блоками любой FPGA являются гибкий программируемый «логический блок» (CLB), окруженный программируемыми «блоками ввода / вывода» с иерархией каналов маршрутизации, соединяющих различные блоки на плате.

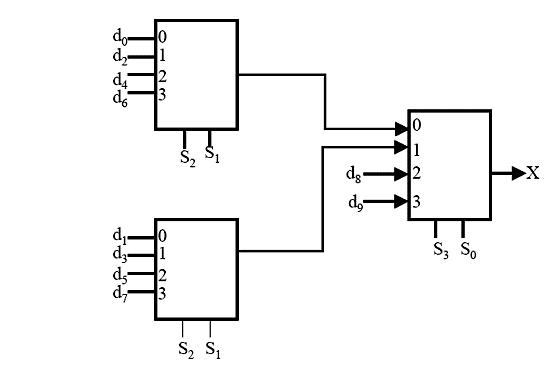

Кроме того, они могут состоять из DLL-библиотек для распределения и управления часами и памяти RAM выделенного блока с основным строительным блоком логической ячейкой. Последняя состоит из генератора входных функций, логики переноса и элементов хранения. Генераторы реализуются в виде справочных таблиц и зависят от введения. Например, Xilinx Spartan II имеет 4 входных LUT с обеспечением каждого 16X1 битным синхронным ОЗУ с использованием мультиплексоров как регистров сдвига для захвата данных в пакетном режиме. Элементы хранения являются чувствительными к краям триггеров или к уровню задвижек.

Фрагмент программирования ПЛИСов:

- Арифметическая логика включает в себя вентиль XOR для работы с полным сумматором и выделением логических линий переноски.

- Блок ввода / вывода и матрица маршрутизации. Этот блок имеет входы и выходы, поддерживающих широкий спектр стандартов и интерфейсов сигнализации.

Базовый блок ввода / вывода показан ниже.

Буфера во входных и выходных путях направляют сигналы во внутреннюю логику и итоговые площадки непосредственно или через триггер. Они настраиваются на соответствие различным поддерживаемым стандартам сигнализации, которые могут быть определены пользователем и установлены извне.

Матрица маршрутизации

На любой сборочной линии медленный сегмент определяет общую производительность. Алгоритмы маршрутизации используются для разработки наиболее эффективных путей обеспечения оптимальной производительности. Маршрутизация осуществляется на разных уровнях, таких, как локальный, маршрутизация общего назначения между различными CLB, маршрутизация ввода-вывода между блоками и CLB, выделенная маршрутизация для определенных сигнальных классов с целью максимизации производительности и Global Routing для распределения тактовых и других сигналов с очень большим разветвлением. Семейства FPGA также имеют большие блочные структуры RAM для дополнения распределенных LUT RAM, размер которых варьируется для различных устройств FPGA.

Проектирование FPGA предполагает в основном тот же подход, что и любая система VLSI, основными этапами которой является проектирование, моделирование поведение, синтез, моделирование после синтеза, трансляция, отображение и маршрутизация, а также последующий анализ, такой как моделирование синхронизации и статический анализ синхронизации. На компьютере дизайн выглядит упорядоченным и уложенным плиткой, однако фактически имеется несовершенное размещение и маршрутизация, что приводит к снижению производительности.

Чтобы повысить производительность FPGA, всегда можно использовать больше транзисторов. Служебная площадь высокая. Установка большего количества транзисторов означает, что возможны масштабные конструкции. Утечка является серьезной проблемой для ПЛИС и в то же время представляет интерес. Использование асинхронной архитектуры FPGA показывает лучшие результаты в сочетании с технологией конвейерной обработки, которая уменьшает глобальные входы и улучшает пропускную способность.

Качество и проблемы ворот

Безопасность системы всегда была главной проблемой, так как код должен раскрываться каждый раз, когда загружался в ПЛИС. Такая гибкость делает FPGA потенциальной угрозой вредоносных модификаций при изготовлении, поэтому шифровании битовых потоков вовремя пришло ему на помощь.

Часто неопытные дизайнеры и пользователи сталкиваются с дилеммой, насколько мощная ПЛИС подходит для их разработок. Производители часто указывают метрики, например, «количество ворот». Например, программирование ПЛИС Xilinx использует 3 метрики для измерения объема FPGA, максимальных логических элементов, максимальных битов памяти и типового диапазона шлюзов. Пока они являются согласованными, миграция между моделями несколько упрощается, но она редко предлагает точное сравнение у различных поставщиков через разнообразие в архитектурах и из-за различий в производительности.

Наилучшим показателем является сравнение типа и количества предоставленных логических ресурсов. В дополнение к этому, разработчик должен полностью осознать, что именно нужно от устройства, поскольку производители могут похвастаться возможностями, которые будут иметь наименьшее значение для работы. Например, Stratix II EP2S180 от Altera имеет около 1,86,576 LUT с 4 входами, а Xilinx Virtex-4 XC4VLX200 содержит соответственно 1,78,176. Однако, если для проектирования нужна только 177 тыс. LUT, это будет достаточно.

Если ОЗУ - это желательная метрика для дизайнера, то ни 6 Мбит Xilinx XC4VLX200, ни 9 Мбит Altera EP2S180 не будут предпочтительнее по сравнению с менее рекламируемой, более старой моделью XC4VFX140 с 9,9 Мбит.

Языки программирования и ПО

Программирование ПЛИС Altera для начинающих стартует с выбора языка. Опция C, C ++ или System C позволяет использовать возможности крупнейших устройств и, в то же время, достижения сходства реалистической графики разработки. Возможность использования на базе C для проектирования FPGA обеспечивается HLS (синтез высокого уровня), который уже много лет находится на грани прорыва с таким инструментом, как Handle-C. В последнее время это стало реальностью благодаря тому, что крупные поставщики Altera и Xilinx предлагают HLS в своих наборах инструментов Spectra-Q и Vivado HLx соответственно.

Доступен ряд других реализаций программирования ПЛИС Altera для начинающих на основе C, таких как OpenCL, который предназначен для разработчиков программного обеспечения, желающих повышения производительности с помощью FPGA без глубокой понимание дизайна FPGA.

Как и в случае с HDL, HLS имеет ограничения при использовании подходов программирования ПЛИС на C также, как и с традиционными HDL, разработчикам приходится работать с подмножеством языка. Например, сложно синтезировать и реализовать системные вызовы, так как нужно убедиться, что все ограничено и имеет фиксированный размер. В HLS приятно то, что можно разрабатывать свои алгоритмы с плавающей запятой и имеется инструмент HLS преобразования плавающей запятой в фиксированную.

Программировать ПЛИС с ПО Xilinx совсем не сложно. Получить его можно, покупая продукты Xilinx, бесплатно или по цене, ориентированной на конкретные модели. Можно получить доступ к видео на профильном сайте, который наглядно показывает процедуру использования. Из всех компаний, которые можно выбрать при поиске программируемых вентильных массивов, Xilinx безусловно лучший из всех. Они являются создателями этого продукта, и в течение многих лет вносили в него улучшения. Фирменное ПО стало более мощным, чем когда-либо прежде.

Этапы проектирования

Обучение программированию ПЛИС можно проводить онлайн, поскольку платформа хорошо представлена в интернете. При настройке ПЛИС первым шагом является проектирование схемы, для которой необходимо знание цифровой электроники. В отличие от программирования, гораздо сложнее начать нарезку кода, если архитектура программы не ясна. Как только станет ясно, что нужно реализовать, приступают к описанию схемы, используя один из языков: Verilog или VHDL.

Факт, который свидетельствует об изменении парадигмы, состоит в том, что они не называются языками программирования ПЛИС, а являются языками описания. Из-за сложности тестирования цифровых схем обычно на этом этапе используются банки тестов, моделирующих поведение оборудования. Этот тип инструментов позволяет видеть состояние сигнала в любой момент и проверять, есть ли переходы с желаемыми результатами.

Третий этап известен как синтез схемы является одним из ключевым. Он выбирает используемые элементы и их взаимосвязь в соответствии с файлами описания. Для этого этапа требуются инструменты, которые в большинстве ситуаций облегчают и автоматизируют задачи.

Аппаратные средства и наладка

Intel Quartus Prime Software Suite Lite Edition — программное обеспечение для проектирования ПЛИС. Оно идеально подходит для начинающих, так как его можно скачать бесплатно, а файл лицензии не требуется. Можно загрузить программное обеспечение на сайте производителя. Файлы имеют большой размер (несколько гигабайт), их загрузка и установка может занять много времени. Чтобы минимизировать время и необходимое дисковое пространство, рекомендуется загружать только те элементы, которые необходимы для пользовательских задач. При запросе, файлах для загрузки, снимают флажок «Select All» и выбирают только Quartus Prime и поддержку Cyclone V устройства.

Алгоритм создания проекта:

- Открывают Мастер нового проекта.

- Выбирают Next > Каталог > Имя > объект верхнего уровня.

- Выбирают каталог для размещения проекта, например, «Blink» и помещают его в папку intelFPGA_lite, но можно разместить его где угодно и нажимают «Далее».

- Когда будет предложено создать каталог, выбирают «Да».

- Выбирают «Пустой проект» и нажимают «Далее».

- Добавляют файлы и «Далее».

- Настраивают семейства, устройства и платы, выбирая следующее: семья - Циклон V, устройство - Циклон V SE, база, название устройства: 5CSEBA6U2317.

- Чтобы выбрать конкретное устройство, нужно нажимать стрелки вверх / вниз, чтобы увидеть список поддерживаемых устройств, пока не появится 5CSEBA6U2317.

- Пользователю может понадобиться расширить поле «Имя», чтобы увидеть полное имя устройства, нажать «Далее».

- При настройке инструмент EDA, используют стандартные инструменты, поэтому никаких изменений не будет, нажимают «Далее» и «Готово». Появится экран резюме.

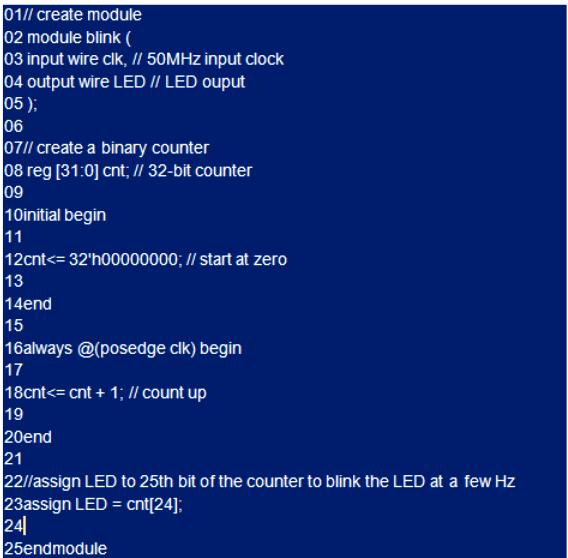

- Создают файл HDL с внедрением Verilog в качестве HDL.

- Переходят на вкладку File (главное окно) и выбирают New.

- Выбирают Verilog HDL File и нажимают кнопку ОК.

- Выбирают «Файл»> «Сохранить как».

- Выбирают имя файла. Это имя файла верхнего уровня, и оно должно совпадать с именем проекта.

- Нажимают «Сохранить».

- Создают модуль Verilog.

- Копируют и вставляют ниже размещенный код Verilog в окно blink.v, а затем сохраняют файл кода.

- Нажимают правой кнопкой мыши «Анализ и синтез», а затем нажимают «Пуск», чтобы выполнить проверку синтаксиса и синтеза кода Verilog.

Если процесс завершается успешно, рядом с анализом и синтезом отображается зеленая галочка. Если ошибка, проверяют синтаксис и убеждаются, что он точно соответствует блоку кода, указанному выше.

Все опытные программисты знают, что сложные программы, даже подпрограммы, не работают правильно с первого раза. Способности к абстракции у человека, основанные на опыте, позволяют ему находить решения, не беспокоясь о мельчайших деталях. Но суровая правда заключается в том, что физическая система, в которую встраиваются программы, требует, чтобы каждая мелочь была учтена, прежде чем все заработает.

С улучшением программных инструментов для разработки ПЛИС в основном от традиционных поставщиков, а также независимых поставщиков инструментов: Synplicity, FPGA — становится день ото дня все более популярной. Теперь ПЛИС начали включать специализированное аппаратное обеспечение необходимых клиенту функций, снижая издержки производителей. Таким образом, в будущем может появиться конкуренция между жесткими и дешевыми системами с гибкими ядрами. Ожидается, что в ближайшей будущем расходы будут снижаться еще больше, поскольку популярность FPGA вырастет в разы.

Производители начали экспериментировать с таким понятием, как встраивание ПЛИС в интегральные микросхемы для создания гибридного устройства. Основное внимание по-прежнему уделяется маршрутизации межсоединений, а в архитектурах CLB наблюдаются меньшие изменения. Поскольку ПЛИС продолжают включать процессоры, новое поколение потребует не только знаний аппаратного обеспечения цифрового дизайна, но и опыта разработчиков в процессе однократного программирования ПЛИС. В целом, ожидается, что FPGA отнимет долю рынка в устройствах ASIC и станет доминирующей технологией, охватывающей множество приложений из различных областей.