Схема сумматора представляет собой один из ключевых элементов цифровой электроники. Это устройство, предназначенное для сложения двоичных чисел. Рассмотрим подробнее определение, классификацию и применение схем сумматоров.

Определение схемы сумматора

Схема сумматора - это комбинационная логическая схема, которая выполняет операцию сложения над входными двоичными числами и выдает результат сложения на выходе.

Функционально сумматор представляет из себя устройство, которое в соответствии с заданным алгоритмом складывает поступающие на его входы двоичные числа и выдает результат сложения.

С точки зрения электроники, схема сумматора представляет собой комбинацию логических элементов (триггеров, мультиплексоров, дешифраторов), соединенных определенным образом и реализующих алгоритм сложения двоичных чисел.

Классификация схем сумматоров

Существует несколько основных типов схем сумматоров, которые различаются по их функциональным возможностям и структуре:

- Полусумматор - суммирует два одноразрядных двоичных числа и выдает результат сложения и перенос в следующий разряд;

Одноразрядный сумматор- суммирует три одноразрядных числа: два складываемых и перенос из предыдущего разряда;- Параллельный сумматор - суммирует сразу несколько разрядов двух многоразрядных чисел;

- Последовательный сумматор - суммирует числа последовательно разряд за разрядом;

Полный сумматор- объединяет в себе параллельный и последовательный сумматоры.

Также сумматоры классифицируют по количеству складываемых чисел:

- Двухвходовые (складывают 2 числа);

- Трехвходовые (складывают 3 числа);

- Многовходовые (складывают более 3 чисел).

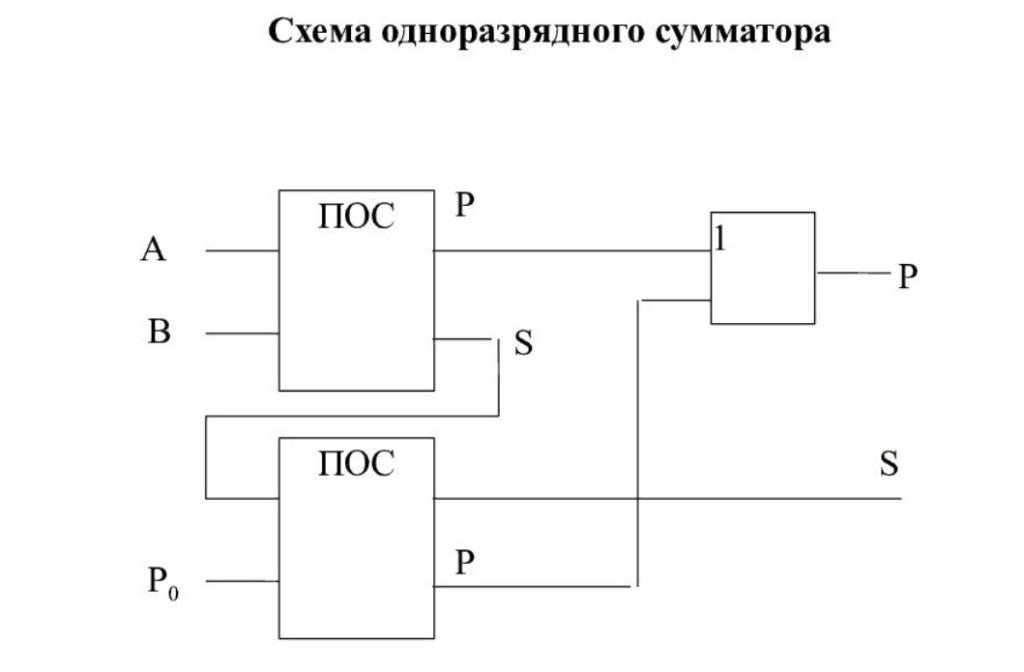

Логическая схема сумматора

Логическая схема сумматора строится на основе элементарных логических элементов И, ИЛИ, НЕ. Например, одноразрядный сумматор может быть построен следующим образом:

- С помощью И вычисляется значение переноса;

- С помощью Исключающего ИЛИ вычисляется результат сложения разрядов;

- С помощью И накапливается перенос от младших разрядов.

Таким образом, из простых логических элементов можно построить сложную схему, выполняющую арифметические операции.

Применение схем сумматоров

Схемы сумматоров широко используются в составе различных цифровых устройств, где требуется выполнять сложение двоичных чисел, в том числе:

- Процессоры - для выполнения арифметических операций;

- Контроллеры - для обработки цифровых сигналов;

- Системы числового программного управления - для сложения координат;

Сумматор сигналов- для суммирования аналоговых и цифровых сигналов в радиотехнических устройствах;Двоичный сумматор- в составе компьютеров для сложения двоичных чисел.

Также сумматоры применяются в качестве отдельных микросхем в различных цифровых устройствах, где нужно производить сложение данных.

Особенности проектирования схем сумматоров

При проектировании схем сумматоров необходимо учитывать ряд особенностей для получения работоспособного и оптимального по быстродействию устройства:

- Выбор элементной базы с учетом быстродействия и надежности;

- Минимизация количества логических элементов;

- Оптимальная топология соединений элементов;

- Грамотное разбиение схемы на отдельные каскады;

- Учет задержек распространения сигналов.

Правильный выбор и расчет параметров при проектировании позволяет создать высокопроизводительную и надежную схему сумматора, оптимально решающую поставленные задачи.

Программная реализация сумматора

Помимо аппаратной реализации, сумматор можно реализовать и программно с использованием высокоуровневых языков программирования.

Например, на языке Python сумматор можно реализовать следующим образом:

def sum(a, b): return a + b x = 1010 y = 0110 sum_result = sum(x, y) print(sum_result) Здесь функция sum() выполняет сложение двух переменных a и b, представляющих двоичные числа. Результат помещается в переменную sum_result.

Такая программная реализация позволяет гибко настроить функционал сумматора и интегрировать его в различные программные системы.

Перспективы развития сумматоров

Развитие вычислительной техники предъявляет все более высокие требования к быстродействию и производительности сумматоров. Основные направления совершенствования схем сумматоров:

- Повышение тактовой частоты работы;

- Увеличение разрядности операндов;

- Оптимизация топологии соединений;

- Использование новых техпроцессов производства интегральных схем;

- Разработка новых архитектурных решений.

Ведутся работы по созданию квантовых сумматоров на основе кубитов, которые позволят значительно расширить возможности вычислений. Дальнейшее развитие схем сумматоров будет способствовать прогрессу в области цифровой электроники и вычислительной техники.

Особенности схемотехнической реализации сумматоров

При разработке схем сумматоров важно учитывать ряд особенностей их схемотехнической реализации для получения работоспособного и эффективного устройства:

- Выбор оптимальной элементной базы - использование быстродействующих логических элементов;

- Минимизация количества используемых элементов для уменьшения задержек;

- Грамотный выбор топологии соединений элементов для сокращения длин соединений;

- Разделение схемы сумматора на отдельные каскады для локализации сбоев;

- Тщательный расчет временных задержек и их синхронизация.

Правильный подбор элементной базы и топологии позволяет добиться высокого быстродействия сумматора и повысить надежность его работы.

Влияние разрядности сумматоров на их производительность

От разрядности сумматора напрямую зависит его производительность и область применения:

- Малоразрядные сумматоры (4-8 разрядов) используются в простых устройствах;

- Сумматоры средней разрядности (16-32 разряда) применяются в бытовой электронике;

- Высокоразрядные сумматоры (64-128 разрядов) используются в вычислительной технике.

Чем выше разрядность, тем сложнее структура сумматора, больше задержки и энергопотребление. Но одновременно растет скорость обработки данных и точность вычислений.

Оптимальный выбор разрядности позволяет получить наилучшее соотношение производительности, сложности и стоимости сумматора для конкретной задачи.

Тестирование и верификация сумматоров

Важным этапом при разработке схем сумматоров является их тестирование и верификация - проверка соответствия техническим требованиям.

Основные методы тестирования:

- Моделирование работы схемы сумматора в САПР;

- Физическое макетирование и измерение параметров;

- Тестирование готовых микросхем на специальном оборудовании.

Проверяются такие параметры, как быстродействие, энергопотребление, надежность, стойкость к сбоям и ошибкам.

Качественное тестирование позволяет выявить и устранить недостатки схемы сумматора перед запуском в производство.

Сумматоры в вычислительных системах

Сумматоры являются ключевыми элементами арифметико-логических устройств во всех типах вычислительных систем - от простых калькуляторов до суперкомпьютеров.

В процессорах сумматоры применяются на нескольких уровнях:

- В арифметико-логическом устройстве для сложения данных;

- В устройстве управления для подсчета адресов команд и данных;

- Во внутренних регистрах процессора.

От быстродействия сумматоров напрямую зависит производительность всего процессора.

Сумматоры в цифровой обработке сигналов

Широко применяются сумматоры в устройствах цифровой обработки сигналов, где необходимо выполнять сложение отсчетов сигнала в режиме реального времени:

- В аналого-цифровых и цифро-аналоговых преобразователях;

- В цифровых фильтрах для суммирования отсчетов;

- В блоках цифровой обработки радиолокационных сигналов.

Высокоскоростные сумматоры критичны для обработки сигналов без искажений и потерь.

Сумматоры в криптографических устройствах

Сумматоры применяются в криптографических устройствах, где требуется выполнять сложение очень больших чисел:

- В схемах генерации псевдослучайных чисел;

- При вычислении криптографических хеш-функций;

- В алгоритмах асимметричного шифрования данных.

Сумматоры, работающие с сотнями и тысячами разрядов, критически важны для криптостойкости.

Перспективы развития сумматоров

Актуальные направления развития схем сумматоров:

- Повышение разрядности до 1024-2048 разрядов;

- Рост тактовой частоты до 1-10 ГГц;

- Создание трехмерных сумматоров;

- Использование новых материалов и техпроцессов;

- Разработка оптических и квантовых сумматоров.

Совершенствование сумматоров позволит расширить возможности обработки данных и повысить производительность вычислительных систем в будущем.